# **OPEN ACCESS INTERNATIONAL JOURNAL OF SCIENCE & ENGINEERING**

# IMPLEMENTATION OF APPROXIMATE AND ACCURATE MULTIPLIERS USING CMFA

<sup>1</sup>SiraparapuSriRamya, <sup>2</sup>P V V Rajesh

<sup>1</sup>*M.Tech, Dept of E.C.E, Jntukakinada, AP India, 9133951289,*

ravisriramya21@gmail.com <sup>2</sup> Assistant Professor, Dept of E.C.E, Jntukakinada, AP India,9492935242,

raj242biet@gmail.com,

------

Abstract: Approximate computing is an emerging approach for decreasing the electricity intake and design complexity in many applications wherein accuracy is not a vital necessity. In this study, extremely-efficient imprecise 4:2 compressor and multiplier circuits as the constructing blocks of the approximate computing structures are proposed. The proposed compressor uses best one majority gate which isn't like the conventional layout methods using AND- OR and XOR logics. Furthermore, most of the people gate is the fundamental logic block in some of the rising majority-friendly nanotechnologies which include quantum dot mobile automata (QCA) and unmarried-electron transistor (SET).

# **I INTRODUCTION**

Optimizations in VLSI have been executed on 3 factors: Area, Power and Timing (Speed). This is carried out in each frontcease and returned-stop of design. In front-cease design, proper description of simplified Boolean expression and getting rid of unused states will lead to decrease the gate/transistor utilization. Partition, Floor making plans, Placement, and routing are carry out in back-end of the design which is done through CAD device. The CAD tool have a specific algorithm for every procedure to supply an area efficient layout similar to Power optimization. Power optimization is to reduce the

strength dissipation of the layout which suffers by operating

voltage, operating frequency, and switching hobby.

Quantum-dot cellular automata (QCA) are an appealing rising era suitable for the improvement of ultra-dense low-energy excessive-overall performance digital circuits. Quantum-dot cell automata (QCA) which employs array of coupled quantum dots to put into effect Boolean good judgment characteristic. The benefit of QCA lies in the extremely high packing densities possible because of the small length of the dots, the simplified interconnection, and the extraordinarily low power put off product. A simple QCA cellular consists of four quantum dots in a square array coupled via tunnel limitations. Electrons are able to tunnel between the dots, but cannot go away the cell. If two extra electrons are positioned inside the cell, Coulomb repulsion will pressure the electrons to dots on contrary corners. There are accordingly two energetically equivalent ground country polarizations may be categorized good judgment "0" and "1". The simple building blocks of the QCA structure are AND, OR and NOT. By using the Majority gate, we are able to lessen the quantity of postpone. I.E via calculating the propagation and generational incorporates.

The dynamic behavior of QCA turned into discussed with the assist of the hart tree approximation [4], Quantum mechanics is likewise concerned in locating out the mobile size and dot radius of an unmarried QCA cell. Hence, QCA have become research hobby to set up as robust CMOS opportunity. During closing a long time, in nanotechnology technology, an exhaustive research has been finished on this domain. QCA remains in infancy level, desires plenty ofstudy for QCA common sense circuit design. The low power reversible good judgment circuit layout, tile based totally logic circuit layout in addition to its defect analysis are prime trouble domain. The ternary computing with QCA is maximum tough project on this area when you consider that no such development is noticed. The multivalued computing, particularly ternary computing is a rising area of studies due the potential blessings like more records garage functionality, quicker mathematics operations, better support for numerical analysis, application of nondeterministic and heuristic methods, communiqué protocol and powerful answer for non-binary issues. It is thought that successful chemically synthesized QCA cells are deposited on the substrate. In this segment 3 not unusual defects that have been analyzed are (a) more cell deposition i.e. More QCA cell/s is/are deposited than the original requirement of mobile association, (b) missing cell deposition/ un-deposited mobile deposition, i.E. The QCA cell/s is/aren't deposited as required in unique design, (c) displaced /out of place cellular deposition, i.e. QCA mobile/s is/are misplaced from the exact position of deposition. These three kinds of defects can also reason fundamental 2 deadly errors in QCA production. The device or gate design using QCA required a permissible disorder tolerance on the above-noted defects such that the tool now not loses its traits. Hence, defect evaluation is becoming most promising problem area in QCA.

Every eighteen months' variety of circuit additives turn out to be double [1] in addition to the industry is now facing a growing vital tendencies of "More-than-Moore", stated within the Semiconductor Industries Association's International Roadmap for Semiconductors [2]. Researchers have to find out a strong alternative of CMOS generation for VLSI design. Nanotechnology turned into found as a sturdy alternative, issue to some confusion and controversy and complicated by the truth that there are evidently occurring nano length materials and different nano size particle, in the range from 1pm all the way down to 10A. Nanotechnologies won its existence in development within subject of microelectronics. Nano mechanical computing factors are scalable in terms of input size and depth of propagation course analyzed the usage of a bounded continuum model.

Quantum Dot Cellular Automata (now and again mentioned definitely as quantum cellular automata, or QCA) are proposed models of quantum computation, that have been devised in analogy to conventional fashions of cellular automata introduced via von Neumann. Standard stable nation QCA cellular design considers the gap between quantum dots to be about 20 nm, and a distance among cells of about 60 nm. Just like all CA, Quantum (-dot) Cellular Automata are based at the simple interplay policies between cells located on a grid. A QCA mobile is constructed from four quantum dots organized in a square sample. These quantum dots are web sites electrons can occupy by using tunneling to them.

# **II LITERATURE SURVEY**

The evolution of electronic information era (IT) and communications has been specifically feasible by non-stop progress in silicon-based totally Complementary Metal Oxide Semiconductor (CMOS) technology. This continuous development has been maintained mainly by way of its dimensional scaling, which ends up in exponential growth in each device density and performance. Thus avoiding further discount size. Dimensional scaling of CMOS transistors is achieving their fundamental physical limits [5]. These Nanodevices take benefit of the quantum mechanical phenomena and ballistic delivery characteristics below decrease deliver voltage and as a result low energy intake. These gadgets are predicted to be used for ultra-excessive density integrated electronic computer systems because of their extremely small length.

However, due to their smaller diameters, the inversion fee modifications from floor inversion to bulk inversion because of quantum confinement. Thus, versions in Nano-twine dimensions due to fabrication imperfections can cause perturbations in the service ability and scattering that degrade the price delivery traits. Also, variations in Nanocord diameters may additionally lead to a version in FET threshold voltage. Reducing variability is therefore a key project in making Nano-cord FETs a feasible era. Furthermore, quantum confinement effects make modeling of Nano-cord transistors a complex hassle. The physics related to the operation of Nano-wire transistors desires to be nicely articulated in order that easy compact models, which includes ballistic delivery and practical sub band parameters, may be advanced for circuit design the use of SPICE-like simulators.

Carbon Nano Tubes (CNTs) have been located in 1991. Due to their specific cloth houses [3], Carbon Nano Tubes (CNTs) have obtained worldwide attention from many studies works. CNTs are grapheme (which is a -dimensional honeycomb lattice of carbon atoms) sheets rolled up into cylinders. They display both metal or semiconducting homes depending at the route how CNTs are rolled up (chirality). Since the bandgap of semiconducting CNTs is inversely proportional to their diameters, threshold voltage may be effortlessly. With their superior cloth residences, along with the awesome mechanical and thermal balance, big current wearing capacity, and high thermal conductivity, the metal Nano-tubes are appealing as future interconnects [3]. Along with those houses, the semiconducting nanotubes additionally display first rate advantages as a channel fabric of highperformance FETs.

Single Electron Transistors (SETs) are very appealing devices for destiny largescale integration, due to their small size and low-energy dissipation at proper speed. The simple structure of SET consists of three-terminals: drain, gate, supply, and the second one gate, is an optional. A schematic of SET is similar to that of traditional MOSFETs. However, SET has a tiny conductive island coupled to a gate electrode with gate capacitance. Source and drain electrodes are related to the island via a tunnel barrier (junction). In SETs small voltage is carried out between the sources and drain electrodes by the "Coulomb blockade" phenomenon [4]. ISO 3297:2007 Certified

Single-electron processes, representing a piece with the aid of a Single-electron ("bit kingdom good had been restrained to laboratory demonstrations. The trouble of the constrained fan out, that's caused by the usage of only a single electron within the definitely Single-electron devices, can be solved by way of modern circuit designs which include the binary selection- diagram. Therefore, the deficiencies of CMOS have caused sizable efforts to locate suitable options and a few of the proposed answers; Nano-scale technology including Tunneling Phase Logic (TPL), Single Electron Tunneling (SET) and Quantum-dot Cellular Automata (QCA) has obtained enormous attention [8].

Resent researches have proposed Quantum-dot possible implementations for QCA cells. As such Quantum-dot cells has presented in [1]. An adiabatic switching paradigm is advanced for clock-managed pipelined QCA architectures. The binary records are saved as electronic charge leading to much less computing. Other investigators were extending the theoretical analysis of QCA arrays. Tonamoto et al. Have proposed opportunity approaches of assembling QCA cells into beneficial devices. Lusth and Jackson have implemented graph theoretic analysis to QCA design. Chen and Porod have advanced sophisticated finite element fashions for gate depleted Quantum-dots in semiconductors that can relate Dot occupancy to precise bias situations.

Investigations related to switching pace and temperature dependence of QCA have been presented in [7]. Orthodox Coulomb blocked and grasp equation dynamic technique has been considered for a semi-infinite shift register designUnidirectionality and Metastability trouble within a QCA twine has been studied, 3Darchitecture is proposed in vicinity of asymmetric spacing in [70]. The classical calculation carried right here has shown that 3D-configuration may also be the way to conquer Metastability issues. While H-reminiscence is a layout evolved mainly for QCA, authors in [1] propose a brand new execution version that mixes with memory for distributing the functionality of CPU at some stage in the memory systems.

Today's QCA is nearly built as 4 dot cells. However, five dot or even six dot QCA designs have additionally been said in [2]. Recent, studies research is focusing for growing low power gadgets. First time, a QCA power dissipation version has been proposed by Timer and Lent in with the aid of which common power dissipation of a standard QCA circuit is divided into two important components, "leakage" and "switching". Power losses throughout clock vacillations (from low to high or high to low) is posited as leakage power and energy losses all through switching length is considered as switching energy [7]. Numerous low energy Adder circuits with the least electricity dissipation were proposed in literature [9]. Additionally, thinking about fault-tolerant troubles, masses of attempts were made to put into effect QCA fault-tolerant Full-Adder cells [8]. In evaluation to counterpart designs the proposed Full-Adder cell has the least strength dissipation. From the complexity, latency and place point of view the proposed adder systems truly excels all the counter components with a considerable superiority

Since in this paintings, each gate level method and a new express interaction technique had been utilized for designing QCA combinational circuits. We trust that the prevailing research work will be of superb interest to the destiny computations.

# **III EXISTING METHOD**

#### **Design of QCA Full-Adder**

There are several QCA full adder implementations available inside the literature and maximum of them use most of the people discount approach. In the proposed full adder implementation simplest the XOR gates are employed for SUM output at the same time as most people logic method is used to obtain the CARRY output. Consider a full adder with three inputs labelled as A, B, and C and the two outputs labelled as SUM and CARRY. The schematics of complete adder is proven in Figure.

Figure .Schematic of Full Adder

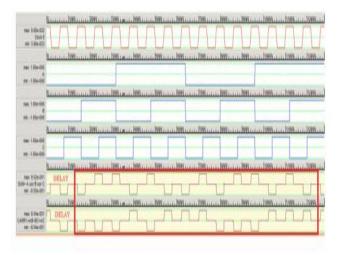

The relationship between the inputs and the outputs are established as: C  $(4.5) \oplus B \oplus A=SUM$  AC (4.6)+BC +AB=CARRY The resulting SUM terminal require best XOR gates, whilst because the CARRY operation may be executed using the unmarried majority gate. The QCA association and the simulation result of the full adder circuit are shown in Figure 3.8 & Figure 3.9 respectively.

Figure QCA layout of Full Adder.

Figure. Schematic of Full Adder.

#### Multiplexer

The characteristic equation of 2:1 multiplexer is given as: BS (4.11) AS  $\Box$  F where A and B are the multiplexer signal inputs, S corresponds to the selector input and F is the multiplexer output sign. The equation (3.11) has two product phrases added collectively, thus we require three majority good judgment gates in which plays the AND operation and the one will offer the OR operation.

Here layout of two:1 multiplexer, selection line (S) is implemented with the assist of forty-five° rotated QCA cells. The benefit of the usage of such line for signal propagation is that wires can be crossed on the identical level without interference or crosstalk. Furthermore, due to the alternating polarization, both the sign and its supplement are effortlessly extracted. Some other gain of this layout is that it requires the minimal clock zones, lesser cells and occupies much less location.

# **IV PROPOSED ARCHITECTURE**

The growing of the density and complexity of nanoscale digital included circuits have caused substantially better power density and heat dissipation in current VLSI chips. The high electricity density will increase the leakage currents and decreases the reliability and lifetime of incorporated circuits. Moreover, the energy intake has grown to be very critical specifically in battery operated portable electronic devices [1]. An emerging paradigm for reducing the energy dissipation is to use approximate computing in applications where a high accuracy isn't a crucial necessity. Computation's errors and imprecisions can be tolerated in those packages, at the same time as having comprehensible and useful effects which can be perceptible sufficient for human cognizance. Actually, with an affordable reduction in preciseness, many circuit parameters along with the number of gadgets, electricity consumption, delay and area can be reduced. Accordingly, approximate computing is a hit answer for immediate computation in errors tolerant programs to attain easier circuits with more electricity performance [2], [3]. It is superb that, as a layout paradigm, approximate computing can be carried out in diverse layout ranges of logic, including transistor, abstraction algorithmic, architecture and software program [4]. Multiplier is one of the most widely used and power hungry arithmetic blocks in many digital structures [5]. Because of the complex shape of hardware multipliers and as they're typically located on the essential path of virtual structures, the use of approximate computing can deliver sizeable improvements regarding the system's performance and strength dissipation [2], [6]. Considering these three steps, partial products discount is the most important step in terms of electricity consumption and region [7]. Efficient circuitry for this stage may be found out with efficient approximate four:2 compressors. Accordingly, many green precise and obscure compressors with different stages of efficiencies in hardware and accuracy associated parameters have already been supplied within the literature [2], [3], [8]–[14]. These approximate compressors sacrifice accuracy for energy to exceptional extents and are beneficial for exceptional imprecise packages. Moreover, good sized research has been conducted inside the vicinity of approximate multipliers focused on approximate partial product technology, handing over promising effects [6]. Scaling of the planar MOSFET has brought about a few critical troubles along with decreased gate manage, draincaused barrier decreasing (DIBL), threshold voltage variation, and extensively high strength densities [15]. The FinFET device with a three-dimensional tri-gate structure has been developed as a hit update for the planar MOSFET. FinFET notably complements gate manipulate, reduces brief channel outcomes, and will increase Ion/Iof f ratio. Moreover, the intrinsic frame of FinFET removes the random dopant fluctuations as a vital element for threshold voltage variations [16]. However, FinFET suffers from self-heating impact and better strength density because the limited narrow fins lower the thermal conductivity of the channel. This leads to a substantially decrease number of transistors and a shorter essential course, which bring about decrease power and propagation put off. It is also noteworthy that as most people common sense is the building block in lots of rising nanotechnologies, our method is also very handy for approximate computing based on nanotechnologies. The circuit parameters are evaluated the use of HSPICE and 7nm FinFET generation. Furthermore, important accuracy and first-rate metrics are investigated for the approximate multipliers the use of MATLAB. It is tremendous that the primary essence of the approximate computing is to decrease the layout complexity and power dissipation drastically in

contrast with the precise systems, while sustaining a sure great. Accordingly, discern of merits (FOMs), considering both pleasant and performance factors, also are calculated for the approximate multipliers. These metrics imply that our layout presents an effective alternate-off among first-rate and efficiency for approximate computing

#### BACKGROUNDS

# FinFET

FinFET is a quasi-planar multi-gate transistor with an ultrathin body. In a FinFET, the gate dominantly controls the thin channel from more than one sides, which results in a smaller subthreshold swing, a decrease DIBL and a higher Ion/Iof f ratio. Moreover, the fully depleted undoped frame of FinFET resolves random dopant fluctuations and leads to a higher carrier mobility. Accordingly, FinFET has emerged as a viable update for the planar MOSFET at deep nanoscale technology [17], [18]. Figure 1 indicates the structure of a trigate FinFET.

TABLE I THE TRUTH TABLE OF PROPOSED APPROXIMATE 4:2 COMPRESSOR

| X4 | <b>X</b> 3 | x <sub>2</sub> | X1 | Carry | Sum | Error distance |

|----|------------|----------------|----|-------|-----|----------------|

| 0  | 0          | 0              | 0  | 0     | 1   | +1             |

| 0  | 0          | 0              | 1  | 0     | 1   | 0              |

| 0  | 0          | 1              | 0  | 0     | 1   | 0              |

| 0  | 0          | 1              | 1  | 0     | 1   | -1             |

| 0  | 1          | 0              | 0  | 0     | 1   | 0              |

| 0  | 1          | 0              | 1  | 1     | 1   | +1             |

| 0  | 1          | 1              | 0  | 0     | 1   | -1             |

| 0  | 1          | 1              | 1  | 1     | 1   | 0              |

| 1  | 0          | 0              | 0  | 0     | 1   | 0              |

| 1  | 0          | 0              | 1  | 1     | 1   | +1             |

| 1  | 0          | 1              | 0  | 0     | 1   | -1             |

| 1  | 0          | 1              | 1  | 1     | 1   | 0              |

| 1  | 1          | 0              | 0  | 1     | 1   | +1             |

| 1  | 1          | 0              | 1  | 1     | 1   | 0              |

| 1  | 1          | 1              | 0  | 1     | 1   | 0              |

| 1  | 1          | 1              | 1  | 1     | 1   | -1             |

#### V PROPOSED APPROXIMATE DESIGNS

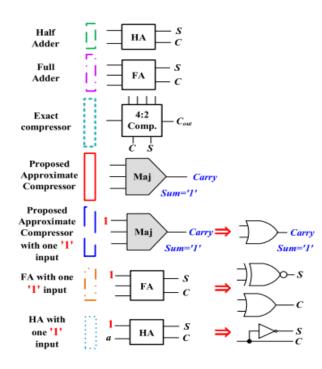

The recent vague compressors have usually been designed primarily based at the AND-OR and XOR logics. Using the XOR common sense increases the overall switching activity [20] and therefore the dynamic strength. On the opposite hand, latest studies have proven that the use of majority good judgment can result in a better layout performance in contrast with the alternative common implementations in emerging nanotechnologies. In this section, our proposed majority-based vague 4:2 compressor and multiplier systems are presented.

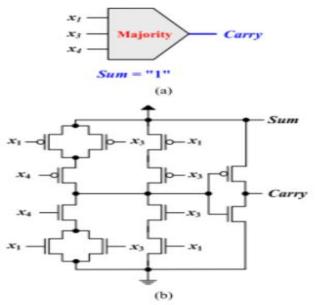

#### **Imprecise 4:2 Compressor**

The proposed approximate 4:2 compressor operates consistent with the equations given in (five)-(7). In our design,

just like other designs like [2], the Cin and Cout alerts are ignored for design efficiency motives. In addition, the inputs x1, x3 and x4 are given to a majority gate that produces the Carry output. Furthermore, Sum is taken into consideration constant and equal to '1', and no extra hardware is required for calculating the Sum fee. This extremely good simplification causes a sizeable discount within the overall energy consumption and propagation postpone of the layout.

$$Cout = Cin = 0$$

(5)

Carry = Majority (x1, x3, x4) = x4 (x1+x3) +x1x3 (6) Sum = VD D (7)

The truth desk of the proposed layout is shown in Table I. A basic situation in designing the approximate blocks is to decrease the error distance (ED) among the consequences of the precise and inexact designs. The error distance is defined because the arithmetic distance between a fake output and its correct value [25]. As an example in Table I, while all inputs are '1', the decimal value of the sum of the inputs is 4. However, the approximate compressor produces '1' for both Carry and Sum outputs, which ends up in a decimal fee of 3 and therefore a mistakes distance of -1. It is high-quality that there may be no fake output with an ED value of two and greater inside the proposed method. These inaccurate outputs can cause unacceptably top notch mistakes.

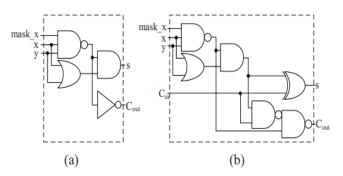

Fig. The proposed approximate 4:2 compressor (a) Block diagram. (b) Circuit design.

The compressor is applied inside the structure of an approximate multiplier. Moreover, the error distances with contrary symptoms together with -1 and +1 can collectively lessen each other's effect in the structure of a multiplier. The proposed approximate four:2 compressors are proven in Fig. 3. The proposed obscure design has a totally easy shape and consists of simplest one majority gate. The majority gate is

designed with 12 transistors primarily based on the complementary good judgment style. The proposed layout superiorly reduces the variety of transistors and important direction duration and therefore the power intake and put off in comparison to its preceding counterparts. The layout of the proposed approximate compressor, designed based totally at the FinFET format design policies said iný [26] and on the fin grid of 7nm, is proven in Fig. Four. According to (1), the riding present day of a FinFET can be enhanced by way of the usage of a couple of parallel fins as channel. However, this additionally significantly will increase the overall switching capacitance because of the three-dimensional shape of FinFET and enlarges the cellular area due to the full-size fin pitch overhead. Accordingly, as the power consumption and place are huge factors in approximate computing, and given that the electrons and holes could have near mobilities in the FinFETs, unmarried-fin gadgets are used. The majority gate is the basic good judgment block in lots of rising technologies which include quantum-dot mobile automata (QCA), unmarried electron tunneling (SET), magnetic tunnel junction (MTJ), nano magnetic common sense (NML), tunneling segment common sense (TPL) and mersister. Moreover, consciousness of most people good judgment based totally on DNA has been established in [28]. The obtainability of efficient majority gate implementations in those rising devices makes our proposed design additionally very convenient for approximate.

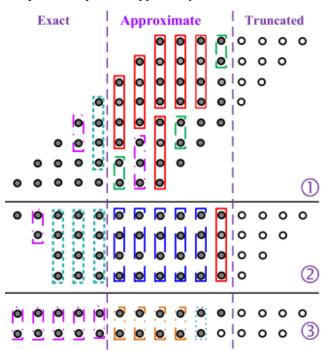

#### **Approximate Multiplier**

In excessive-overall performance multipliers the reduction level, as the maximum crucial and energy-hungry stage, is carried out using compressors [7]. Using approximate compressors in this stage results in an approximate multiplier [2]. The standard shape of an approximate 8-bit Dadda multiplier, based totally on the 4:2 compressors ignoring Cin and Cout, has been defined in [2]. In this structure, the partial merchandise is generated using an array of the AND gates and are decreased in particular based on the approximate compressors. Finally, inside the final level, a ripple delivers adder (RCA) generates the final products. In this structure, to improve the performance and efficiency of the approximate multiplier with a negligible effect on its preciseness, the primary four least vast columns of the partial products can be truncated [12]. Moreover, the usage of genuine computing for the excessive substantial bits can lead to a significantly better accuracy [12]–[14]. However, the usage of specific compressors reduces the performance of the approximate multiplier. Furthermore, obtaining a preciseness more than a sure stage but with a higher electricity consumption isn't always preferred in approximate programs. Therefore, to make an effective alternate-off between the preciseness and overall performance parameters for approximate computing, we use actual compressors for the last five excessive huge bits at the output. Accordingly, as shown in Fig. Five, best 4 of all 16 compressors are actual, which notably complements the accuracy with a low hardware cost. In step one, 3 half ofadders, two complete-adder and six proposed obscure compressors are utilized to reduce the partial products into at most four rows. It is first rate that the 1/2 adder and complete adder cells with the traditional complementary good judgment style [31] are used in this level. In the second one level, a full adder, three exact compressors [8] and 6 proposed imprecise compressors are used. However, 5 of those compressors (distinctive with dashed strains) have one '1' input common sense, as the Sum outputs of the compressors inside the preceding step are identical to '1'. As a three-enter majority gate with one '1' input operates as a two-input OR gate, these 12-tarnsistor compressors are changed with conventional OR gates with most effective six transistors. As an end result, seven AND gates are decreased from the partial product generator degree of the proposed multiplier. In the RCA step, the first module is a 1/2 adder with one '1' input, which may be changed with simply an inverter gate as illustrated in Fig. 5. Moreover, because the three-enter XOR and majority gates with one '1' input function as two-input XNOR and OR gates, respectively, every of the subsequent four full adders with one '1' input (Sum of the previous step compressor) are changed with a two-enter XNOR (Sum) and a -input OR (Cout). It is amazing that the six-transistor CMOS+ design presented in [31] are applied for two-input XNORs. Accordingly, through making use of the proposed obscure compressor, the put off, range of the transistors (as a criterion for the circuit complexity) and consequently the overall electricity consumption of the complete multiplier are appreciably decreased.

Fig. Partial product reduction circuitry of the proposed approximate multiplier.

#### VI ACCURACY-CONTROLLABLE MULTIPLIER

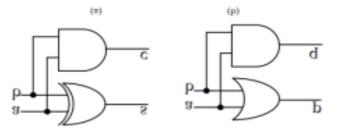

A usual multiplier includes 3 parts: (i) partial product generation the usage of an AND gate; (ii) PPR the usage of an adder tree; and (iii) addition to provide the final end result the usage of a CPA. Power intake and circuit complexity are dominated through the PPR [6], and the multiplier's vital path is dominated by using the propagated convey chain inside the CPA [7]. This section is organized as follows. Section III-A explains how the partial product layer is simplified via the approximate tree compressor. Section III-B introduces the CMA. Finally, Section III-C affords the overall shape of the accuracy controllable approximate multiplier, which makes use of the proposed adder and tree compressor. A. Approximate Tree Compressor Figure 1(a) indicates a correct 1/2 adder, for which the following equation in which, and + denote concatenation and addition, respectively. The price c is generated by means of a b and s is generated by can be generated via a b. Based on the above, don't forget the fundamental common sense cell proven in Fig. 1(b), for which the subsequent equations can be obtained: This is known as an incomplete adder mobile (iCAC). Table I indicates the truth tables for an accurate 1/2 adder and an iCAC. Note that the bit role of c and that of s, p, and q are exceptional. As can be seen, q is identical to c. While p isn't always equal to s, the appropriate sum may be acquired with the aid of adding p and q, so the iCAC isn't an approximate adder but an element of a specific adder. By extending the above equation to bits, the following equation can be obtained: wherein A, B, P, and Q are -bit values, the bits of which correspond to a, b, p, and q, respectively. A row of 8 iCACs, used for 8-bit inputs, is proven in Fig. 2. Consider the example of an eight-bit adder with the two inputs A = 01011111 and B = 00110110. The correct sum S is 10010101, at the same time as the row of iCACs produces P = 01111111 and Q = 00010110. Again, it is obtrusive that the following holds: While S is received from P and Q, P may be used as an approximation for S, and Q can be used as a mistakes healing vector for the approximate sum P.

Fig. (a) Accurate half adder and (b) incomplete adder cell.

| TABLE I. | TRUTH TABLES FOR ACCURATE HALF ADDER AND |

|----------|------------------------------------------|

|          | INCOMPLETE ADDER CELL.                   |

|        |              |           |                                                  | Output                                                    | s                                            |                                                |    |

|--------|--------------|-----------|--------------------------------------------------|-----------------------------------------------------------|----------------------------------------------|------------------------------------------------|----|

|        | Inp          | outs      | Accurate                                         | half adder                                                | iC                                           | CAC                                            |    |

|        | a            | b         | с                                                | s                                                         | q                                            | р                                              |    |

|        | 0            | 0         | 0                                                | 0                                                         | 0                                            | 0                                              |    |

|        | 0            | 1         | 0                                                | 1                                                         | 0                                            | 1                                              |    |

|        | 1            | 0         | 0                                                | 1                                                         | 0                                            | 1                                              |    |

|        | 1            | 1         | 1                                                | 0                                                         | 1                                            | 1                                              |    |

|        |              |           |                                                  |                                                           |                                              |                                                |    |

|        |              |           |                                                  |                                                           |                                              |                                                | L. |

|        | $b_7 a_7$    | $b_6 a_6$ | b <sub>5</sub> a <sub>5</sub> b <sub>4</sub>     | $\begin{bmatrix} a_4 & b_3 & a_3 \\ & & \\ \end{bmatrix}$ | $\begin{bmatrix} b_2 & a_2 \\ \end{bmatrix}$ | b <sub>1</sub> a <sub>1</sub> b <sub>0</sub> a | 0  |

|        | <b>†</b> † Γ | ╤╪╁╷      | ╤╡┧┌╒╡                                           | ┥┎╤╡┥┎╴                                                   | ╡┥┌╴                                         | ╪╁┌╤╪┧                                         | Л  |

| $\Box$ | M            | X         | JJJ                                              | 1TT                                                       | N                                            |                                                | 1  |

| +      | +            |           |                                                  |                                                           | ++                                           | +++                                            |    |

| <br>97 | P7 0         | 6 P6      | <br>q <sub>5</sub> p <sub>5</sub> q <sub>4</sub> | $            p_4 q_3 p_3 q_2$                             | $p_2 q_1$                                    | $\mathbf{p}_1 \mathbf{q}_0 \mathbf{p}_0$       | 9  |

|        |              |           |                                                  |                                                           |                                              |                                                | r  |

|        | Two          | o 8-bit o | utputs :                                         |                                                           |                                              |                                                |    |

|        | Ap           | proxim    | ate sum :                                        | $P = \{p_{7}, p_{6}, p_{5}, p_{4}\}$                      | $p_{3}, p_{2}, p_{1}, p_{1}$                 | <b>b</b> <sub>0</sub> }                        |    |

|        | Er           | ror reco  | very vector : Q                                  | $Q = \{q_{7}, q_{6}, q_{5}, q_{4},$                       | $q_{3}, q_{2}, q_{1}, q_{1}$                 | 0}                                             |    |

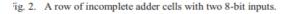

By extending the row of iCACs from two to inputs, /2 Ps and /2 Qs are received. If the sum of the /2 Qs is used rather than the /2 Qs themselves, the variety of Qs is decreased to 1. Remember that P is always more than or same to S, and Q is same to C. By exploiting these records, OR gates may be used to generate the approximate sum of the /2 Qs without huge loss of accuracy. This approximate sum is referred to as the accuracy repayment vector and is denoted by means of V. This technique is called approximate tree compressor (ATC). An ATC with inputs is known as an ATC- , and the structure of an ATC with 8 inputs (ATC-8) is proven in Fig. 3. The rectangles represent rows of iCACs and the variety of iCACs in every row (rectangle) is depending on the bit width of the inputs. For example, if there are 8 -bit inputs (D1, D2, ..., D8), 4 rows of iCACs are required to build a bit ATC-eight. This reconstruction generates 4 approximate sums, P1, P2, P3, and P4, and four error restoration vectors, Q1, Q2, Q3, and Q4. OR gates generate the accuracy compensation vector V. As an end result, the 8 inputs were decreased to 5.

Fig. 3. Structure of an approximate tree compressor with eight inputs.

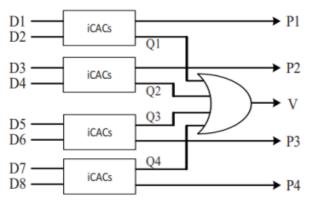

#### **Carry-maskable Adder**

A CMA is proposed to control the accuracy flexibly and dynamically. A Otherwise, when mask\_x is 1, S is equal to x b and Cout is equal to x y. In other words, the operation of the proposed half adder can be controlled by the active-low signal mask\_x. When mask\_x is disabled (=1), it functions as an accurate half adder, and when mask\_x is enabled (=0), Cout is masked to 0 and it functions as an OR gate with output S. The operation of the proposed full adder is similar to the half adder: when mask\_x is disabled (=1), it functions as an accurate full adder, and when mask\_x is enabled (=0), Cout is equal to C in and S is the output of an OR gate.

# **Overall Structure**

An -bit multiplier includes rows, each of which has partial merchandise (PP), so there are PPs in overall. Using the ATC- introduced inside the previous phase, the rows may be replaced rows. Figure five suggests an example of an eight-bit multiplier with \$\$ PPs. The PPR is performed in three degrees (Stage 1, Stage 2, and Stage 3) and the CPA is executed in Stage 4. The PP generation step is not shown. Each dot represents a PP. The least extensive bit (right side) is bit 0, and the maximum vast bit (left aspect) is bit 14. The solid rectangles in Stage 1 constitute ATCs and the dashed rectangles represent rows of seven iCACs. Every row of iCACs consists of PPs that are not processed: for instance, the PP at position 0 in the first row and the one at role eight in the 2d row of the first iCAC block in ATC-8 are not processed. In Stage 1, eight rows of PPs are decreased to four rows (P1, P2, P3, and P4) and one accuracy compensation vector (V1) via an ATC-8. The four rows are in addition reduced to two rows (P5 and P6) and another accuracy reimbursement vector (V2) by using an ATC-4. A very last row of iCACs then processes P5 and P6 and generates P7 and Q7. In precis, Stage 1 makes use of an ATC-8, an ATC-4, and a row of 7 iCACs to compress the \$\$ PPs to 4 rows (P7, V1, V2, and Q7).

Fig. 4. (a) Carry-maskable half adder, (b) Carry-maskable full adder.

Fig. 5. Structure of an 8-bit multiplier with 8 × 8 partial products.

In Stage 2, there are 4 PPs for every of bits four to ten. In order to achieve a decrease path delay, OR gates are used to sum V1 and V2 approximately. The empty circles for V1 and V2 represent the bits which might be summed the use of OR gates. Seven OR gates are required in total and the four rows are compressed to three. In Stage three, full adders and half adders are used to compress the 3 rows to 2. Two half adders are required for bits 1 and thirteen, and 11 complete adders are required for bits 2 to twelve. Addition the usage of a CPA is needed after PPR to supply the very last end result. For an eight-bit Wallace tree multiplier, the length of the CPA is eleven [7]. In our proposed multiplier, the period of the CPA is 13. In Stage four, the CPA is split into 3 components so one can reduce the length of the deliver propagation. Since the decrease bits aren't vast for accuracy, bits 0 to four are defined as the truncated element and three OR gates are used to generate the values for bits 2, 3, and 4 of the very last result. Because there may be no perform from the truncated component, the duration of the CPA is reduced to ten. Since the top bits are the maximum enormous for accuracy, bits 12 to fourteen are defined as the correct part, and three correct adders are used to generate the values for those bits of the final result. The accuracy-controllable element lies among the truncated and accurate elements. This element is crucial for each important route postpone and accuracy. In Stage four, bits five to eleven within the CPA are changed through a 7-bit CMA. Note that every 1-bit CMA has a mask x sign. Given a cost for %, the % higher bits in the accuracy-controllable component are configured as a %-bit CPA and the decrease bits are configured as (&! %) 2-input OR gates through dealing with the seven mask\_x indicators as it should be. When % = 7, it capabilities as a 7-bit CPA, and when % = 0, it features as seven 2-input OR gates. For every bit of S this is generated by using a 2-input OR gate, power intake is reduced due to the fact the switching interest is decreased in a number of the common sense gates. Furthermore, the maximum postpone of the CMA is decreased.

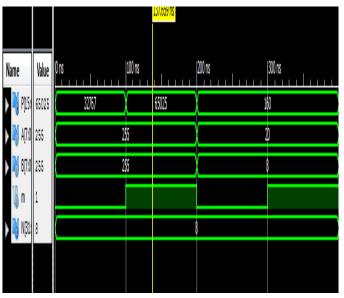

#### VII RESULTANALYSIS

Many an increasing number of famous programs, along with photograph processing and popularity, are inherently tolerant of small inaccuracies. These packages are computationally disturbing and multiplication is their essential arithmetic feature, which creates an opportunity to exchange off computational accuracy for reduced strength intake. Approximate computing is a good technique for error tolerant applications because it can change off accuracy for power, and it presently plays an important function in such application domains [1]. Different error-tolerant programs have one of a kind accuracy requirement, as do one of a kind software phases in a utility. If multiplication accuracy is fixed, energy will be wasted whilst excessive accuracy isn't always required. This way that approximate multipliers need to be dynamically reconfigurable to suit the unique accuracy necessities of different program phases and packages. This paper makes a specialty of an approximate multiplier design which could manage accuracy dynamically. A delivermakeable adder (CMA) is proposed that may be dynamically configured to function as a conventional bring propagation adder (CPA), a set of bit-parallel OR gates, or an aggregate of the 2. This configurability is realized by means of overlaying convey propagation: the CPA in the closing stage of the multiplier is replaced through the proposed CMA. An approximate tree compressor is applied to reduce the accumulation layer depth of the partial product tree. Our approach introduces a term representing the energy and accuracy requirements which simplifies the partial product reduction (PPR) thing as wanted. An approximate multiplier is designed the use of the proposed adder and compressor. This multiplier, together with a traditional multiplier and the previously studied approximate multipliers, changed into carried out in Verilog HDL the usage of a forty-five-nm library to assess the strength intake, critical path postpone, and design place. Compared with the traditional Wallace tree multiplier, the proposed approximate multiplier decreased energy consumption by using between 47.3% and fifty-six.2% and the important course put off by using between 29.9% and 60. 5%, relying on the required computational accuracy. In addition, its design place became 44.6% smaller. Comparisons with the set up approximate multipliers, none of that have any dynamic reconfigurability, display that the proposed multiplier supplied the nice change-off of strength and delay towards accuracy. All the multiplier designs are then evaluated in a real photograph processing application.

**DESIGN SUMMARY**

| Device Utilization Summary (estimated values) |      |           |             |     |  |  |  |  |

|-----------------------------------------------|------|-----------|-------------|-----|--|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |     |  |  |  |  |

| Number of Slice LUTs                          | 4982 | 204000    |             | 2%  |  |  |  |  |

| Number of fully used LUT-FF pairs             | 0    | 4982      |             | 0%  |  |  |  |  |

| Number of bonded IOBs                         | 131  | 600       |             | 21% |  |  |  |  |

The above result represents the synthesis implementation by using the Xilinx ISE software. From the above table, it is observed that only 4982 look up tables are used out of available204000. It indicates very less area (2%) was used for the proposed design.

# TIME SUMMARY

| LUT2:I0->0                               | 1 | 0.043 | 0.000 | div1/Madd GND 49 o GND 49 o a |  |  |

|------------------------------------------|---|-------|-------|-------------------------------|--|--|

| MUXCY:S->0                               | 1 | 0.230 | 0.000 | div1/Madd_GND_49_0_GND_49_0_a |  |  |

| XORCY:CI->O                              | 2 | 0.251 | 0.347 | div1/Madd_GND_49_0_GND_49_0_a |  |  |

| LUT4:I2->0                               | 1 | 0.043 | 0.000 | div1/Msub_n0258_Madd_lut<30>  |  |  |

| MUXCY:S->0                               | 0 | 0.230 | 0.000 | div1/Msub_n0258_Madd_cy<30> ( |  |  |

| XORCY:CI->O                              | 1 | 0.251 | 0.289 | div1/Msub_n0258_Madd_xor<31>  |  |  |

| LUT5:I4->0                               | 1 | 0.043 | 0.279 | Mmux_out110 (out_0_OBUF)      |  |  |

| OBUF:I->0                                |   | 0.000 |       | out_0_OBUF (out<0>)           |  |  |

| Total 54.238ns (31.895ns logic, 22.343ns |   |       |       |                               |  |  |

(58.8% logic, 41.2% route)

The above result represents the time consumed such as path delays by using the Xilinx ISE software. The consumed path delay is 54.238ns.

# POWER SUMMARY

| A                 | B                | C | D       | E          | F             | G           | H               | I | J       | K         | L           | M           | N           |

|-------------------|------------------|---|---------|------------|---------------|-------------|-----------------|---|---------|-----------|-------------|-------------|-------------|

| Device            |                  |   | On Ohip | Power (W)  | llsed         | Available   | Utilization (%) |   | Supply  | Summary   | Total       | Dynamic     | Quiescent   |

| Family            | Vitex7           |   | Logic   | 0.000      | 3709          | 204000      | 2               |   | Source  | Votage    | Current (A) | Current (A) | Current (A) |

| Pat               | xc7xx330t        |   | Signals | 0.000      | 4570          | -           | -               |   | Vccint  | 1.000     | 0.086       | 0.000       | 0.086       |

| Package           | ffg1157          |   | l)s     | 0.000      | 131           | 600         | 22              |   | Vocaux  | 1.800     | 0.030       | 0.000       | 0.030       |

| Temp Grade        | Commercial       | ٧ | Leakage | 0.143      |               |             |                 |   | Vcco18  | 1.800     | 0.001       | 0.000       | 0.001       |

| Process           | Typical          | ٧ | Total   | 0.143      |               |             |                 |   | Vocbram | 1.000     | 0.002       | 0.000       | 0.002       |

| Speed Grade       | 3                |   |         |            |               |             |                 |   |         |           |             |             |             |

|                   |                  |   |         |            | Effective TJA | Max Ambiert | Junction Temp   |   |         |           | Total       | Dynamic     | Quiescent   |

| Environment       |                  |   | Themal  | Properties | (C/W)         | (C)         | (C)             |   | Supply  | Power (W) | 0.143       | 0.000       | 0.143       |

| Ambient Temp (C)  | 25.0             |   |         |            | 1.4           | 84.8        | 25.2            |   |         |           |             |             |             |

| Use custom TJA?   | No               | ٧ |         |            |               |             |                 |   |         |           |             |             |             |

| Custom TJA (C/W)  | NA               |   |         |            |               |             |                 |   |         |           |             |             |             |

| Aiflow (LFM)      | 250              | ٧ |         |            |               |             |                 |   |         |           |             |             |             |

| Heat Sink         | Medium Profile   | V |         |            |               |             |                 |   |         |           |             |             |             |

| Custom TSA (C/W)  | NA               |   |         |            |               |             |                 |   |         |           |             |             |             |

| Board Selection   | Medium (10"x10") | ٧ |         |            |               |             |                 |   |         |           |             |             |             |

| # of Board Layers | 12to 15          | ٧ |         |            |               |             |                 |   |         |           |             |             |             |

| Custom TJB (C/W)  | NA               |   |         |            |               |             |                 |   |         |           |             |             |             |

The above result represents the power consumed by using the Xilinx ISE software. The consumed power is 0.143uw.

# VIII CONCLUSION

An accuracy-controllable approximate multiplier has been proposed on this paper that consumes much less strength and has a shorter crucial course delay than the conventional layout. Its dynamic controllability is realized through the proposed CMA. The multiplier became evaluated at both the circuit and application ranges. The experimental outcomes reveal that the proposed multiplier turned into able to deliver substantial power financial savings and speedups at the same time as keeping a extensively smaller circuit vicinity than that of the traditional Wallace tree multiplier. Furthermore, for the identical accuracy, the proposed multiplier introduced greater improvements in each energy consumption and essential route delay than other formerly studied approximate multipliers. Finally, the capability of our proposed multiplier to manipulate accuracy becomes confirmed with the aid of an application level evaluation. The power saving may be increased if the following criterion is considered in the future low power VLSI design. Number of bits considered may be increased in the encoding scheme.Power can be reduced by improving the partial product compression ratio.

# **IX FUTURE SCOPE**

The power saving may be increased if the following criterion is considered in the future low power VLSI design.

Number of bits considered may be increased in the encoding scheme.

Power can be reduced by improving the partial product compression ratio.

#### REFERENCES

[1] C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernestein, "Quantum cellular automata," *Nanotechnology*, vol. 4, no. 1, pp. 49–57, 1993.

[2] M. T. Niemer and P. M. Kogge, "Problems in designing with QCAs Layout = Timing," *Int. J. Circuit Theory Appl.*, vol. 29, no. 1, pp. 49–62, 2001.

[3] J. Huang and F. Lombardi, *Design and Test of Digital Circuits by Quantum-Dot Cellular Automata*. Norwood, MA, USA: Artech House,2007.

[4] S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A dynamic range unbiased multiplier for approximate applications," in Proc. IEEE/ACMInt. Conf. Comput.-Aided Design (ICCAD), Austin, TX, USA, 2015, pp. 418–425.

[5] W. Liu, L. Lu, M. O'Neill, and E. E. Swartzlander, Jr., "Design rules for quantum-dot cellular automata," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2011, pp. 2361–2364. [5] K. Kim, K. Wu, and R. Karri, "Toward designing robust QCA architectures in the presence of sneak noise paths," in *Proc. IEEE Design, Autom. Test Eur. Conf. Exhibit.*, Mar. 2005, pp. 1214–1219.

[6] A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and analysis of approximate compressors for multiplication," IEEE Trans.Comput., vol. 64, no. 4, pp. 984– 994, Apr. 2015. International Journal of VLSI design & Communication Systems (VLSICS) Vol.10, No.1, February 2012

[7] A. B. Kahng and S. Kang, "Accuracy-configurable adder for approximate arithmetic designs," in Proc. 49th Design Autom. Conf. (DAC), Jun. 2012, pp. 820–825.

[8] K. Kong, Y. Shang, and R. Lu, "An optimized majority logic synthesis mythology for quantum-dot cellular automata," *IEEE Trans. Nanotechnology*.vol. 9, no. 2, pp. 170–183, Mar. 2010.A. Momeni, J.Han, P.Montuschi and F. Lombardi,

"Design and Analysis of Approximate Compressors for

Multiplication", IEEE Trans. Computers, vol. 64, no. 4, pp.984-994, April 2015.

A. Momeni, J.Han, P.Montuschi and F. Lombardi, "Design and Analysis of Approximate Compressors for Multiplication", IEEE Trans. Computers, vol. 64, no. 4, pp.984-994, April 2015.

[9] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approx-imate adders," IEEE Trans. Comput.-Aided Design In-tegr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

[10] K. Walus, G. A. Jullien, and V. S. Dimitrov, "Computer arithmetic structures for quantum cellular automata," in *Proc. Asilomar Conf.Sygnals, Syst. Comput.*, Nov. 2003, pp. 1435–1439.